Top 6 RISC-V Chips with Multi-core Design and AI Accelerator for AI and ML

Перевод: https://www.dfrobot.com/blog-13462.html

Топ 6 чипов RISC-V с многоядерным дизайном и ускорителем ИИ для ИИ и МО

DFRobot

05 декабря 2023

8410

Принятие RISC-V, свободной и открытой архитектуры набора команд для компьютеров, впервые представленной в 2010 году, стремительно ускоряется, в первую очередь благодаря растущему спросу на искусственный интеллект (ИИ) и машинное обучение (МО). Исследовательская фирма Semico прогнозирует ошеломляющий ежегодный рост на 73,6 процента в количестве чипов с использованием технологии RISC-V, с прогнозом в 25 миллиардов ИИ чипов к 2027 году, что принесет доход в размере 291 млрд долларов США. Эта статья выделит популярные продукты на основе архитектуры RISC-V для ИИ и МО, доступные на нынешнем рынке.

Преимущества архитектуры RISC-V в сравнении с x86 и ARM для ИИ и МО

*Гибкость набора инструкций RISC-V.* Более высокая гибкость набора инструкций RISC-V хорошо соответствует потребности в более быстрых итерациях и большей вычислительной мощности в алгоритмах ИИ. Набор инструкций RISC-V может быть настроен и адаптирован под конкретные требования приложений, что позволяет лучше подстраиваться под разные алгоритмы ИИ, включая глубокое обучение и нейронные сети.

*Преимущество по эффективности процессоров RISC-V.* Лицензиаты выбирают RISC-V за его высокую эффективность по сравнению с традиционными микропроцессорами. В сравнении с ARM и x86, RISC-V демонстрирует примерно в 3 раза большую вычислительную производительность на ватт.

*Гибкость единого IP в комбинации или переконфигурации.* IP RISC-V может быть “декомпозирован” сильнее, чем ARM, что позволяет решать различные сценарии проектирования чипов. Это также приносит более высокую масштабируемость архитектуре RISC-V, позволяя дизайнерам свободно разбирать модули, как игрушки LEGO, и комбинировать их для создания идеальных чипов.

*Короткое время перехода между ARM и RISC-V.* Переход между ARM и RISC-V аналогичен переходу программиста, знающего структуры данных, между языками C и Python. Меняются лишь инструкции, в то время как общая философия дизайна остается неизменной. Дизайнер, хорошо разбирающийся в архитектуре ARM, может понадобиться всего около двух недель для перехода к разработке на RISC-V.

Продукты на базе чипов RISC-V для ИИ и МО

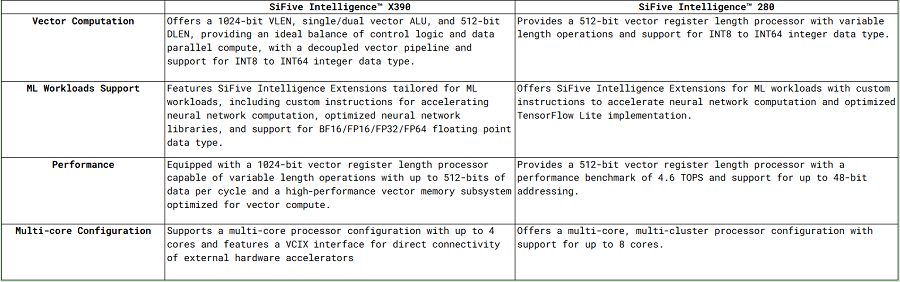

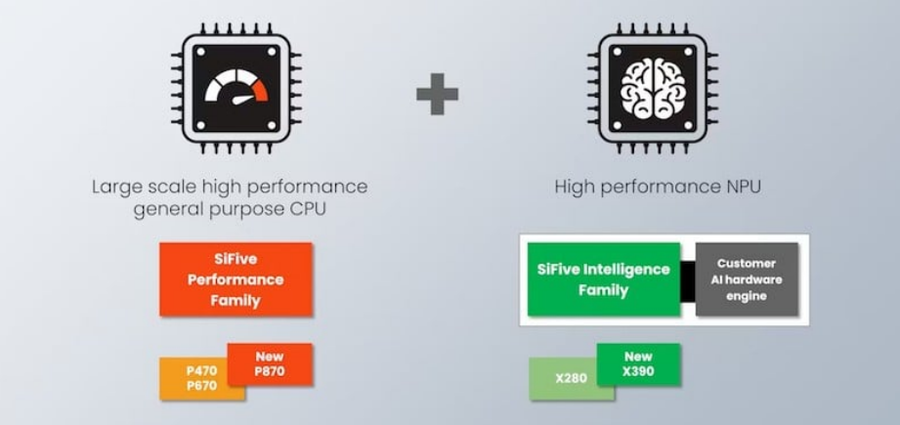

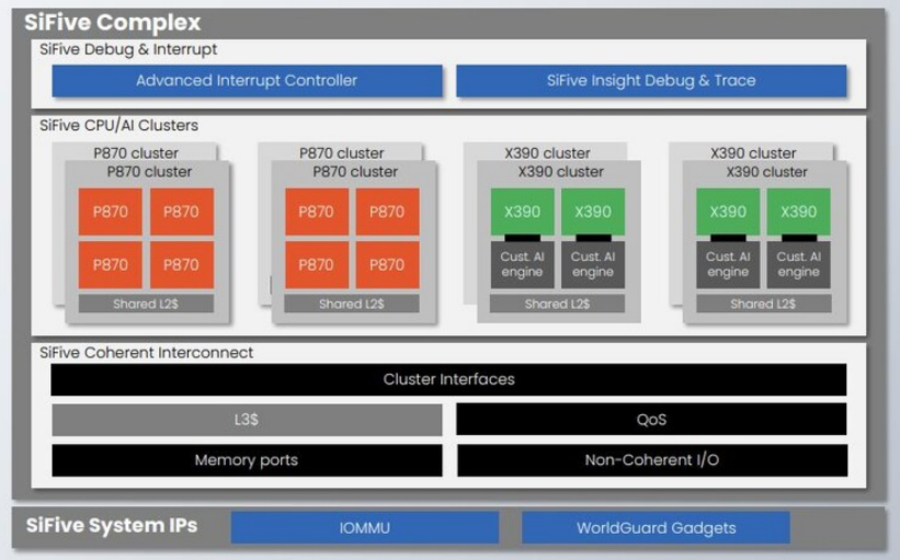

SiFive Intelligence™ X390

Процессор Intelligence X390 разработан для удовлетворения растущих потребностей приложений искусственного интеллекта и машинного обучения. Он основывается на базе X280 с ключевыми улучшениями, которые значительно повышают его вычислительные возможности. Обладая конфигурацией с одним ядром, процессор обеспечивает четырехкратное улучшение векторных вычислений благодаря двойному векторному ALU и удвоенной длине вектора, что дает четырехкратное увеличение пропускной способности данных. Кроме того, процессор интегрирует технологию VCIX от SiFive, позволяя компаниям добавлять пользовательские векторные инструкции или аппаратное ускорение для беспрецедентной гибкости оптимизации производительности. Улучшенные возможности векторных вычислений делают процессор X390 особенно подходящим для задач обучения и работы нейронных сетей.

Ключевые особенности

*Расширения SiFive Intelligence для нагрузки МО*

*Процессор с регистром длиной 512 бит*

*Показатели производительности*

*5.75 CoreMarks/МГц*

*3.25 DMIPS/МГц*

*4.6 SpecINT2k6/ГГц*

*Построен на доказанном на кремнии ядре серии U7*

*64-битный ISA RISC-V*

*Конвейер с двойной выдачей и 8 стадиями*

*Высокопроизводительная векторная подсистема памяти*

*Адресация до 48 бит*

*Конфигурация многоядерная, многокластерного процессора, до 8 ядер*

SiFive Performance P870

SiFive Performance P870 – это ядро процессора, основанное на архитектуре RISC-V и являющееся частью серии SiFive Performance. Разработано для высокопроизводительных вычислений и приложений в центрах обработки данных, ядро процессора SiFive Performance P870 обладает мощными вычислительными возможностями и гибкой настройкой. Используя открытую архитектуру команд RISC-V, это ядро процессора может удовлетворить требования различных сложных вычислительных задач, включая искусственный интеллект, аналитику больших данных и высокопроизводительные вычисления. SiFive Performance P870 стремится предоставить клиентам высокопроизводительные, энергоэффективные процессоры, чтобы удовлетворить растущие потребности в вычислительных ресурсах.

Ключевые особенности

*Полная поддержка спецификаций профиля RVA22 RISC-V и Vector 1.0, а также векторной криптографии, что позволяет запускать 64-битные приложения на ОС, таких как Linux и Android.*

*Прорывные производительности RISC-V*

*Согласованные многосердцевые, многокластерные конфигурации процессоров, до 16 ядер*

*Наивысшая производительность среди коммерчески лицензируемых процессоров RISC-V*

*12 SpecINT2k6/ГГц (процессор P870)*

*2x 128b VLEN RVV*

*Векторная криптография и расширения гипервизора*

*IOMMU и AIA*

*Невключающая L3 кэш-память*

*Проверенная безопасность RISC-V WorldGuard*

*Архитектурные особенности серии P800*

*64-битное ядро RISC-V с обширной поддержкой виртуальной памяти*

*Конвейер с четырьмя стадиями и внеочередной обработкой, настроенный на масштабируемую производительность*

*Приватные кэши L2 и страимость для улучшенной производительности памяти*

*SECDED ECC с сообщением об ошибках*

Эти два процессора различаются по целям проектирования и прикладной направленности. SiFive Performance P870 главным образом используется для высокопроизводительных вычислений и приложений в центрах обработки данных, в то время как SiFive Intelligence™ X390 предназначен для пограничного искусственного интеллекта и машинного обучения.

T-Head XuanTie C910

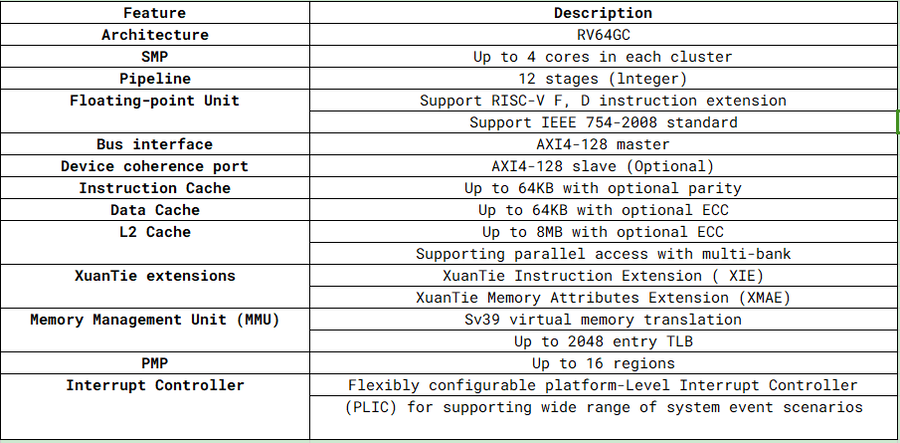

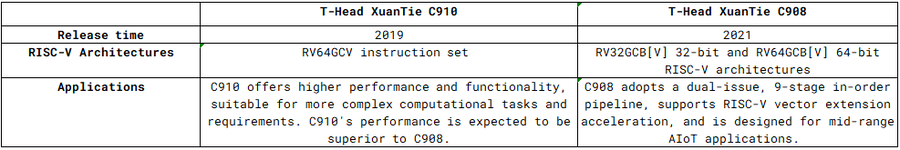

T-Head XuanTie C910 демонстрирует ведущие в отрасли показатели производительности в управлении потоком, вычислениях и частоте благодаря архитектурным и микроархитектурным инновациям. Процессор C910 основан на наборе инструкций RV64GC и реализует технологию XIE (XuanTie Instruction Extension). C910 использует передовой 12-стадийный конвейер с внеочередной обработкой нескольких инструкций, обладающий высокой частотой, IPC и энергоэффективностью. C910 поддерживает аппаратную когерентность кэша. Каждый кластер содержит 1-4 ядра. C910 поддерживает интерфейс шины AXI4 и включает порт когерентности устройств. C910 использует систему виртуальных адресов SV39 с технологией XMAE (XuanTie Memory Attributes Extension). В дополнение к этому, C910 включает стандартные контроллеры прерываний CLINT и поддерживает совместимый с RV интерфейс отладки и мониторы производительности.

Ключевые особенности

*T-Head XuanTie C910*

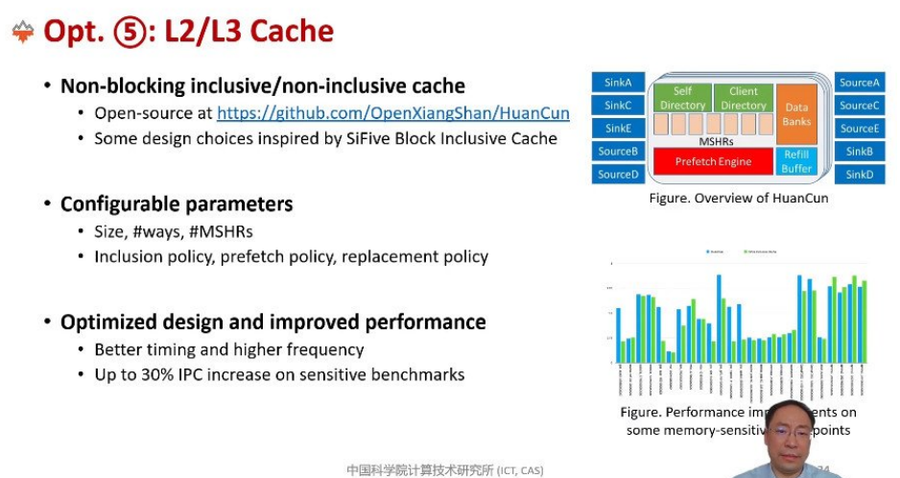

XiangShan Open-source 64-bit RISC-V Processor

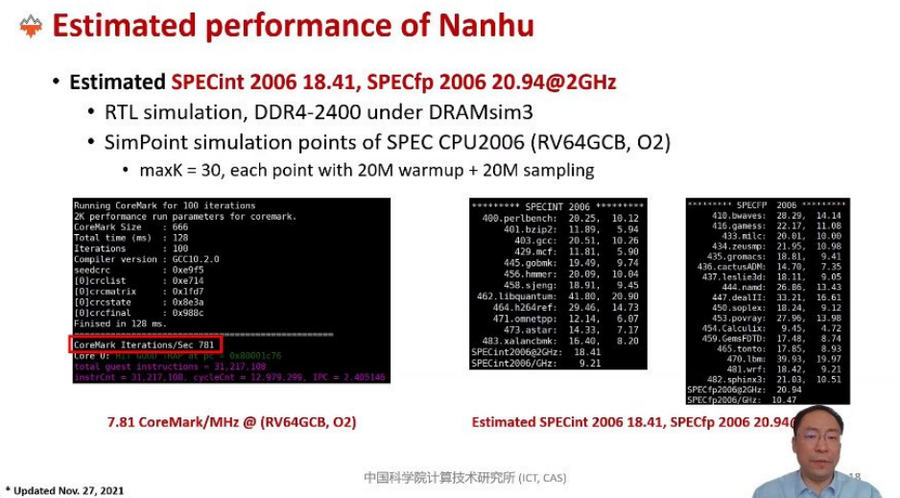

В мае 2023 года Китайская академия наук выпустила второе поколение открытого высокопроизводительного ядра процессора RISC-V “Xiangshan” (архитектура Nanhu), которое было завершено в сентябре 2022 года и передано в производство в июне 2023 года. Это ядро процессора использует процесс 14 нм от SMIC, с основной частотой 2 ГГц, счетом SPEC CPU 10/ГГц, двухканальной памятью DDR, двухканальным интерфейсом PCIe, интерфейсом USB, интерфейсом HDMI и другими функциями. Его полная мощность превосходит ARM Cortex-A76, делая его самым мощным ядром RISC-V в мире.

Ключевые особенности

*XiangShan Open-source 64-bit RISC-V Processor*

Чип Esperanto ET-SoC-1

Чип Esperanto ET-SoC-1 интегрирует более 1000 ядер процессоров RISC-V и 24 миллиарда транзисторов, включая 1088 энергоэффективных 64-битных ядер RISC-V с упорядоченной обработкой ET-Minion и 4 высокопроизводительных 64-битных ядра RISC-V с внеочередной обработкой ET-Maxion. Каждое ядро оснащено векторным/тензорным блоком, с ожидаемыми рабочими частотами от 500 МГц до 2 ГГц. Также, чип включает 1 процессор обслуживания RISC-V, более 160 миллионов байт встроенной SRAM для кэшей и памяти scratchpad, и интерфейсы, поддерживающие большие внешние памяти, включая LPDDR4x DRAM и eMMC flash, PCIe x8 Gen4 и другие обычные интерфейсы ввода-вывода. При пиковой мощности ET-SoC-1 способен достигать от 100 до 200 триллионов операций в секунду (TOPS), при этом обычно потребляя менее 20 ватт мощности. Отличительной чертой решения Esperanto является использование нескольких низкопотребляющих SoC-чипов вместо одного большого SoC. Это может быть привлекательным энергоэффективным решением для рекомендаций машинного обучения в крупных центрах обработки данных.

Ключевые особенности

*Интеграция более 1000 ядер процессоров RISC-V*

*Включение 1088 64-битных ядер RISC-V с упорядоченной обработкой ET-Minion*

*Включение 4 высокопроизводительных 64-битных ядер RISC-V с внеочередной обработкой ET-Maxion*

*Состоит примерно из 24 миллиардов транзисторов*

*Специально разработан для ИИ и машинного обучения*

*Обеспечивает исключительные возможности параллельной обработки*

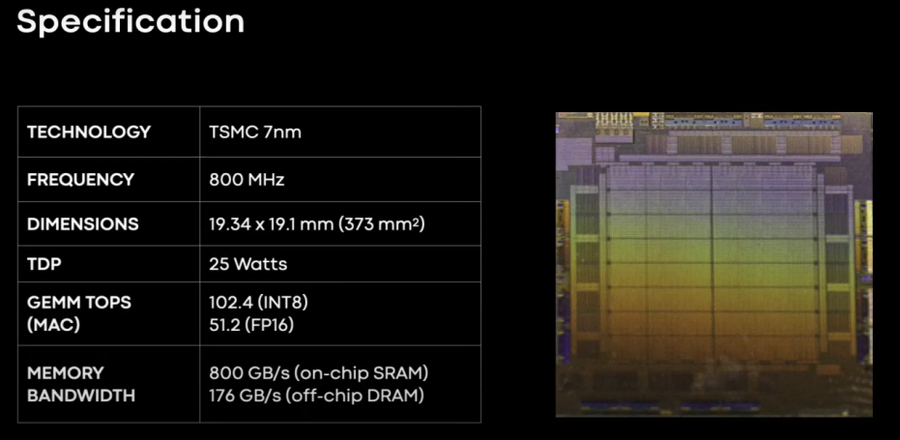

Meta Training Inference Accelerator (MTIA) Chip

MTIA разработан Meta для более эффективной обработки их нагрузок ИИ. Ядра процессоров основаны на архитектуре открытого набора команд RISC-V. Чип является специализированной интегральной схемой (ASIC), построенной для улучшения эффективности рекомендательных систем Meta, например, понимания контента, канала новостей Facebook, генеративного ИИ и ранжирования рекламы, все из которых зависят от рекомендательных моделей глубокого обучения (DLRM), требующих больших ресурсов памяти и вычислительной мощности.

Ключевые особенности

*Meta Training Inference Accelerator (MTIA) Chip*

Первое поколение ASIC MTIA было разработано в 2020 году специально для внутренних нагрузок Meta. Чип был изготовлен с использованием 7-нм процесса TSMC и работает на частоте 800 МГц, обеспечивая 102,4 TOPS при точности INT8 и 51,2 TFLOPS при точности 16-битного плавающего числа. Он также имеет тепловой дизайн мощностью (TDP) 25 Вт. Чип MTIA является частью полностекового решения, которое включает в себя кремний, PyTorch и рекомендательные модели; все это совместно разработано для предоставления полностью оптимизированной системы ранжирования для клиентов Meta. Выпуск их первого ИИ-чипа MTIA – значительное событие. Это еще больше подогревает гонку на рынке ИИ-оборудования и способствует эволюции оборудования, специально разработанного для ИИ-приложений.

Заключение

Чипы, упомянутые в статье, обладают многоядерным дизайном, каждое ядро которого предлагает высокую производительность и энергоэффективность. Они поддерживают многопоточные операции, что позволяет выполнять несколько задач одновременно. Кроме того, они все поддерживают наборы инструкций Single Instruction Multiple Data (SIMD), которые могут ускорять параллельные задачи обработки данных, такие как обработка изображений и векторные вычисления. По мере развития отрасли, мы полагаем, что продукты на основе архитектуры RISC-V будут играть все более важную роль в приложениях ИИ и МО, обеспечивая надежную основу для будущих технологических инноваций и приложений.

Ошибки:

- Минорные грамматические ошибки и некорректные формулировки были исправлены, чтобы улучшить ясность и читабельность текста.